ADT7518

Rev. A | Page 9 of 40

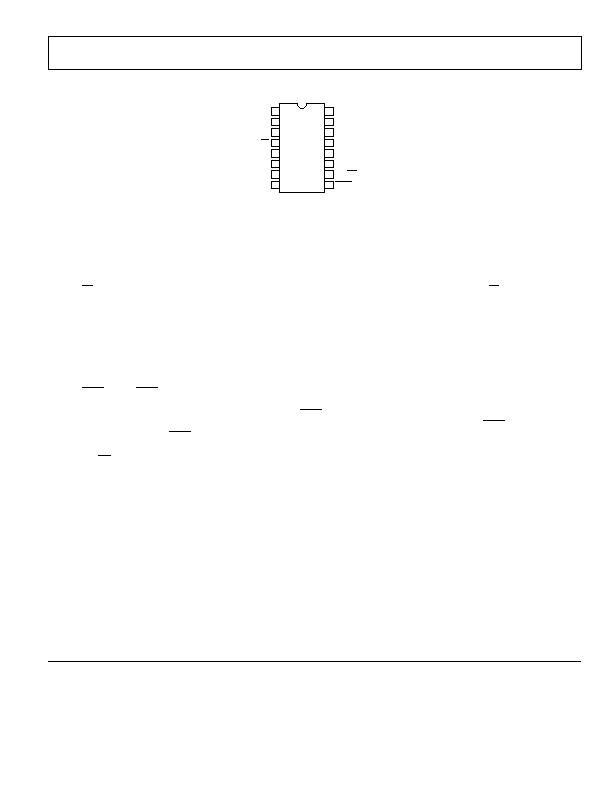

PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

ADT7518

TOP VIEW

(Not to Scale)

V

OUT

-B 1

V

OUT

-C

16

V

OUT

-A 2

V

OUT

-D

15

V

REF

-IN 3

AIN4

14

CS 4

SCL/SCLK

13

GND 5

SDA/DIN

12

V

DD

6

DOUT/ADD

11

D+/AIN1 7

INT/INT

10

D/AIN2 8

LDAC/AIN3

9

Figure 7. Pin Configuration QSOP

Table 5. Pin Function Descriptions

Pin

No. Mnemonic Description

1

V

OUT

-B

Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

2

V

OUT

-A

Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

3

VREF-IN

Reference Input Pin for All Four DACs. This input is buffered and has an input range from 1 V to VDD.

4

CS

SPI Active Low Control Input. This is the frame synchronization signal for the input data. When CS

goes low, it enables

the input register, and data is transferred in on the rising edges and out on the falling edges of the subsequent serial

clocks. It is recommended that this pin be tied high to V

DD

when operating the serial interface in I

2

C mode.

5

GND

Ground Reference Point for All Circuitry on the Part. Analog and digital ground.

6

VDD

Positive Supply Voltage, 2.7 V to 5.5 V. The supply should be decoupled to ground.

7

D+/AIN1

D+. Positive Connection to External Temperature Sensor. AIN1. Analog Input. Single-ended analog input channel.

Input range is 0 V to 2.25 V or 0 V to VDD.

8

D/AIN2

D. Negative Connection to External Temperature Sensor.

AIN2. Analog Input. Single-ended analog input channel. Input range is 0 V to 2.25 V or 0 V to V

DD

.

9

LDAC

/AIN3 LDAC

. Active Low Control Input. Transfers the contents of the input registers to their respective DAC registers. A

falling edge on this pin forces any or all DAC registers to be updated if the input registers have new data. A minimum

pulse width of 20 ns must be applied to the LDAC

pin to ensure proper loading of a DAC register. This allows simul-

taneous update of all DAC outputs. Bit C3 of the Control Configuration 3 register enables the LDAC

pin. Default is

with the LDAC

pin controlling the loading of the DAC registers.

AIN3. Analog Input. Single-ended analog input channel. Input range is 0 V to 2.25 V or 0 V to V

DD

.

10

INT/INT

Over Limit Interrupt. The output polarity of this pin can be set to give an active low or active high interrupt when

temperature,VDD, or AIN limits are exceeded. The default is active low. Open-drain outputneeds a pull-up resistor.

11

DOUT/ADD SPI Serial Data Output. Logic output. Data is clocked out of any register at this pin. Data is clocked out on the falling

edge of SCLK. Open-drain outputneeds a pull-up resistor.

ADD. I

2

C Serial Bus Address Selection Pin. Logic input. A low on this pin gives the address 1001 000; leaving it floating

gives the address 1001 010; and setting it high gives the address 1001 011. The I

2

C address set up by the ADD pin is

not latched by the device until after this address has been sent twice. On the eighth SCL cycle of the second valid

communication, the serial bus address is latched in. Any subsequent changes on this pin will have no effect on the

I

2

C serial bus address.

12

SDA/DIN

SDA. I

2

C Serial Data Input/Output. I

2

C serial data to be loaded into the parts registers and read from these registers is

provided on this pin. Open-drain configurationneeds a pull-up resistor.

DIN. SPI Serial Data Input. Serial data to be loaded into the parts registers is provided on this pin. Data is clocked into

a register on the rising edge of SCLK. Open-drain configurationneeds a pull-up resistor.

13

SCL/SCLK

Serial Clock Input. This is the clock input for the serial port. The serial clock is used to clock data out of any register of

the ADT7518 and also to clock data into any register that can be written to. Open-drain configurationneeds a pull-

up resistor.

14

AIN4

Analog Input. Single-ended analog input channel. Input range is 0 V to 2.25 V or 0 V to V

DD

.

15

V

OUT

-D

Buffered Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

16

VOUT-C

Buffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT30TS00-MAH-T

SENSOR DGTL TEMP I2C/SMBUS 8WDFN

AT30TSE002B-MAH-T

SENSOR DGTL TEMP I2C/SMBUS 8WDFN

BD3504FVM-TR

IC REG CTRLR SGL POS ADJ 8MSOP

BD3521FVM-TR

IC REG CTRLR SGL 1.5V MSOP8

BD9153MUV-E2

IC REG TRPL BCK/LINEAR 24VQFN

CAT2300VP2-GT3

IC SENSE FET CONTROLLER 8TDFN

CAT34TS02VP2GT4A

IC TEMP SENSOR 2K MEMORY 8TDFN

CAT6095VP2-GT4

IC TEMP SENSOR STAND ALONE 8TDFN

相关代理商/技术参数

ADT7518ARQZ-REEL

制造商:Analog Devices 功能描述:Temp Sensor Analog Serial (4-Wire, SPI, I2C) 16-Pin QSOP T/R

ADT7518ARQZ-REEL7

制造商:Analog Devices 功能描述:Temp Sensor Analog Serial (4-Wire, SPI, I2C) 16-Pin QSOP T/R

ADT7519

制造商:AD 制造商全称:Analog Devices 功能描述:SPI-/I2C-Compatible, Temperature Sensor,4-Channel ADC and Quad Voltage Output

ADT7519ARQ

制造商:Analog Devices 功能描述:Temp Sensor Digital Serial (4-Wire, SPI, I2C) 16-Pin QSOP

ADT7519ARQ-REEL

制造商:Analog Devices 功能描述:Temp Sensor Digital Serial (4-Wire, SPI, I2C) 16-Pin QSOP T/R

ADT7519ARQ-REEL7

制造商:Analog Devices 功能描述:Temp Sensor Digital Serial (4-Wire, SPI, I2C) 16-Pin QSOP T/R 制造商:Analog Devices 功能描述:TEMP SENSOR DGTL SERL (4-WIRE, SPI) 16QSOP - Tape and Reel

ADT7519ARQZ

功能描述:IC TEMP SNSR QUAD DAC 16-QSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 热管理 系列:- 标准包装:3,000 系列:- 功能:温度开关 传感器类型:内部 感应温度:85°C 分界点 精确度:±6°C(最小值) 拓扑:ADC(三角积分型),比较器,寄存器库 输出类型:开路漏极 输出警报:是 输出风扇:是 电源电压:2.7 V ~ 5.5 V 工作温度:-55°C ~ 125°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) 其它名称:ADT6501SRJZP085RL7-ND

ADT7519ARQZ1

制造商:AD 制造商全称:Analog Devices 功能描述:SPI/I2C Compatible, Temperature Sensor, Four Channel ADC and Quad Voltage Output DAC